0-315-00451-7. Bibliothèque nationale National-Library of Canada du Canada Division des thèses canadiennes **Canadian Theses Division** Ottawa, Canada 48010 K1A ON4 PERMISSION TO MICROFILM - AUTORISATION DE MICROFILMER Please print or type — Écrire en lettres moulées ou dactylographier Full Name of Author --- Nom complet de l'auteur ALCON Date of Birth Country of Birth Lieu-de naissance less and St NJ.S. BZN Title of Thesis -- Titre de la thèse FUNDAMENTAL DIGITAL COMPUTER SKILLS FOR ELECTRONIC TECHNICIANS University — Universite SAINT MARY'S UNIVERSITY Degree for which thesis was presented — Grade pour lequel cette thèse fut présentée MASTER OF ARTS Year this degree conferred — Année d'obtention de ce grade Name of Supervisor - Nom du directeur de thèse Permission is hereby granted to the NATIONAL LIBRARY OF L'autorisation est, par la présente, accordée à la BIBLIOTHÈ-QUE NATIONALE-DU CANADA de microfilmer cette thèse et de CANADA to microfilm this thesis and to lend or sell copies of the film. prêter ou de vendre des exemplaires du film. The author reserves other publication rights, and neither the L'auteur selréserve les autres droits de publication; ni la thèse ni de longs extraits de celle-ci ne doivent être imprimés ou thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission. autrement reproduits sans l'autorisation écrite de l'auteur. Date Signature

#### National Library of Canada Collections Development Branch

Canadian Theses on Microfiche Service

#### Bibliothèque nationale du Canada Direction du développement des collections

Service des thèses canadiennes sur microfiche

# NOTICE

The quality of this microfiche is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially • if the original pages were typed with a poor typewriter ribbon or if the university sent us a poor photocopy.

Previously copyrighted materials (journal articles, published tests, etc.) are not filmed.

Reproduction in full or in part of this film is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30. Please read the authorization forms which accompany this thesis.

# THIS DISSERTATION HAS BEEN MICROFILMED EXACTLY AS RECEIVED

La qualité de cette microfiche dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

AVIS

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de mauvaise qualité.

Les documents qui font déjà l'objet d'un droit d'auteur (articles de revue, examens publiés, etc.) ne ' sont pas microfilmés.

La reproduction, même partielle, de ce microfilm est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30. Veuillez prendre connaissance des formules d'autorisation qui accompagnent cette thèse.

# LA THÈSE À ÉTÉ MICROFILMÉE TELLE QUE NOUS L'AVONS REÇUE

# FUNDAMENTAL DIGITAL COMPUTER

SKILLS FOR ELECTRONIC TECHNICIANS

# A Thesis

Presented to

the Faculty of Graduate Studies

Saint Mary's University

In Partial Fulfillment

of the Requirements for the Degree

Master of Arts (Education)

### bv

John R. Balcom

March 1980

Č

John R. Balcom 1980

TE O N 1

L

| Abstract <sup>1</sup> . |                                                                  | ii       |

|-------------------------|------------------------------------------------------------------|----------|

| Acknowledge             | ements                                                           | iii      |

| List of Tal             | bles                                                             | vi       |

| CHAPTER                 |                                                                  | •        |

| I.                      | INTRODUCTION                                                     | <b>1</b> |

| -                       | b<br>Definition of Terms                                         | 2        |

| 2                       | Delimitations                                                    | 4        |

|                         | Limitations                                                      | 5        |

| II.                     | HISTORY OF COMPUTERS                                             | 7        |

|                         | Birth of the Microcomputer                                       | 10       |

|                         | Summary                                                          | 12       |

| 111.                    | HISTORY OF ELECTRONIC TRAINING<br>IN REGIONAL VOCATIONAL SCHOOLS |          |

| -                       | Summary                                                          | 16       |

| IV.                     | PROJECTIONS FOR THE COMPUTER<br>INDUSTRY                         | 18       |

|                         | Microcomputers                                                   | 18       |

| • —                     | Data Communications                                              | 20       |

|                         | Word Processing                                                  | 22       |

| <b>v.</b>               | INDUSTRY REQUIREMENTS,<br>DACUM CHART                            | 25       |

| VI.        | REVIEW OF TRAINING PROGRAMS                | $\sim$ |

|------------|--------------------------------------------|--------|

| · · · · ·  | IN DIGITAL COMPUTER                        |        |

| 2.         | ELECTRONICS                                | 30     |

|            | Practical Microprocessors by               |        |

| ÷.,        | Hewlett-Packard                            | 33     |

|            | Advantages                                 | 34     |

|            | Disadvantages                              | 35     |

| •          | Individual Learning Programs               |        |

|            | in Microprocessors by                      |        |

|            | HeathKit Continuing Education              | 35     |

|            | Advantages                                 | 37     |

|            | Disadvantages                              | 37     |

|            | Summary                                    | 38     |

| •          | Selection of the AIM 65                    |        |

|            | Microcomputer'                             | 38     |

| VII.       | SUMMARY OF THE PROPOSED<br>COURSE OF STUDY | 41     |

| •          | •                                          |        |

| •          | Table of Contents for                      |        |

| •          | Digital/Computer Technology                | 45     |

| VIII.      | CONCLUSIONS/RECOMMENDATIONS                | 60     |

|            | Recommendations                            | 66     |

| •          | Conclusions                                | . 67   |

|            | · · · · · · · · · · · · · · · · · · ·      | 2      |

| REFERENCES | ••••••                                     | 69     |

| •          | Footnotes 1 - 12 (inclusive)               | 70     |

|            | Footnotes 13-17 (inclusive)                | 71     |

Bibliography

72

| APPENDIX A | Digital/Computer_Technology<br>Course of Study                                                                 | 77  |

|------------|----------------------------------------------------------------------------------------------------------------|-----|

| APPENDIX B | Glossary                                                                                                       | 374 |

| APPENDIX C | Letters of permission and<br>Information                                                                       | 382 |

| APPENDIX D | Course outlines for "Practical<br>Microprocessors" and<br>"Individual Learning Programs<br>in Microprocessors" | 387 |

φ.

There has been a rapid increase in the use of computers by our society: This increase has been brought about by the introduction of microprocessors and large scale integrated circuits, and the associated reduction in cost per gate.

Internationally recognized computer experts are predicting that we are entering a new age, "the computer age". Many more technicians will be required to install, test and maintain computers.

The purpose of this thesis is to: 1 ) determine the job skills (digital/computer) of technicians employed in computer electronics, 2 ) propose a course of study that will train electronic technicians in fundamental digital/computer skills.

The Dacum method of occupational analysis was used to determine computer technicians skills. Representatives from several companies met for a three day workshop and developed the Dacum chart which lists the job skills for a computer technologist.

Two programs designed to teach fundamental skills in microprocessors (Hewlett-Packard and Heathkit) were reviewed to determine if they were suitable for use in Regional Vocational Schools.

The researcher has presented a course of study that will teach fundamental digital computer skills. This course is

ABSTRACT

developed around a microcomputer trainer using the 6502 chip. It is designed to prepare the student for employment in the digital/computer industry.

The rapid explosion of microprocessors in our society will require a workforce trained in digital/computer technology. This training can and should be carried out in Regional Vocational Schools.

## ACKNOWLEDGEMENTS

I wish to thank Dr. B.E. Davis for his direction of this study and Dr. D.L. Burt for editorial assistance.

I wish to thank the following: Mr. Louis Gervais for his expert advice on microcomputers; Mr: John Wilson who was instrumental in developing the Dacum chart for computer technology. Finally I would like to thank my family for their support and understanding; my wife Alice, who typed the original manuscript, my son Bruce for constructive criticism and my

daughters Karen and Carla.

LIST OF TABLES

| TABLE |  |

|-------|--|

|-------|--|

I. Faster, Smaller Cheaper ..... 13

II. Dacum Chart ..... 29A

•

#### **I** INTRODUCTION

The evolution of electronic technology over the past twenty years has been so rapid it has often been called a revolution, and even compared to the industrial revolution. Not only are computers in the process of changing society but they have also changed many of the techniques used in modern day research. At the heart of the electronic revolution lies the microprocessor, essentially a complete computer on a single chip no bigger than a dime. Already these devices have been found in games, consumer products, intelligent terminals, sophisticated test equipment to name just a few. In the future we will find microprocessors in our cars, telephones, washing machines or in any device where electronic control can be applied.

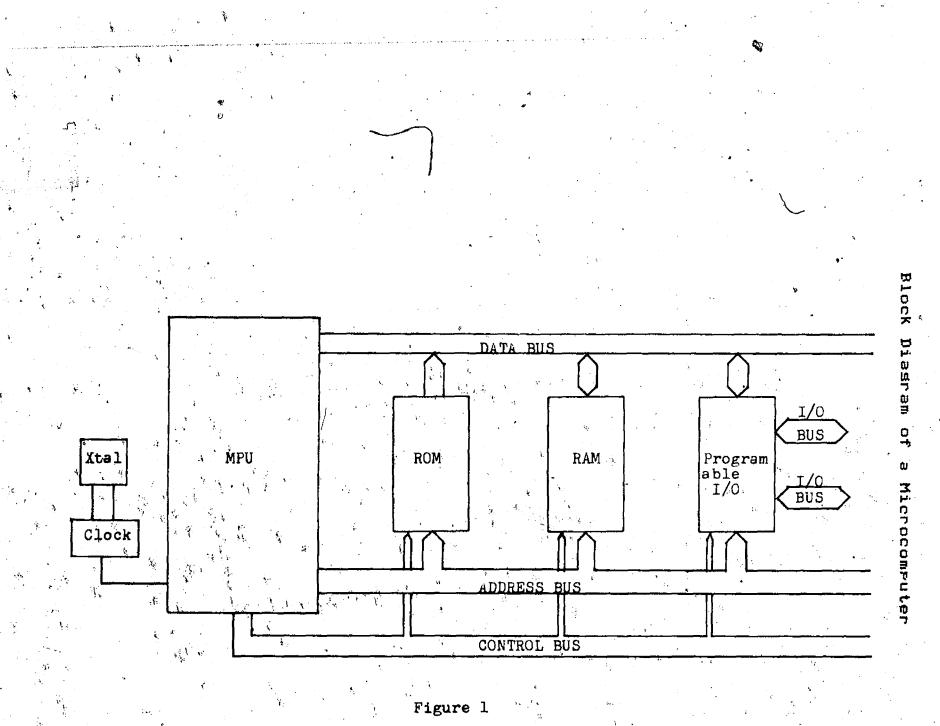

A microcomputer, the type used in business and industry, will consist of a microprocessor (the heart of the computer), memory and various input/output dewices. These computers are constructed from Large Scale Integration (LSI) chips. These chips contain in excess of one hundred thousand (100,000) transistors on a quarter inch square slab. The speed of the computer has. been increased until it will perform in excess of one billion operations per second. All this, and it will fit in a good size suitcase.

Electronic and computer workers are in short supply. "A group of eighty companies are raising \$250,000 for a direct mail advertising magazine to lure electronic engincering graduates and technicians to the Ottawa region".<sup>1</sup> Projections for this region alone are that the Digital and Computer industries will require 4000 to 5000 new

Will the youth of Nova Scotia be adequately trained to fill computer related jobs or will they only be qualified to fill rapidly disappearing jobs, using technology of the 50's and the 60's?

The purpose of this thesis is to: 1) determine the job skills (digital/computer) required by the electronics industry, 2) propose a course of study that will train technicians in fundamental digital/computer skills.

# DEFINITION OF TERMS

Assembly Language: A computer language that uses mnemonic names to stand for one or more machine language instructions. The advantage of using assembly language instead of a high level language, such as Basic, is speed of execution, but a high level-language is usually easier for a human being to understand. DACUM: (Developing A Curriculum) is an approach to the development of curriculum combined with an evaluation process for occupational training programs. It was created initially in a joint effort by the Experimental Projects Branch, Canada Department of Manpower and Immigration, and General Learning Corporation of New York.<sup>2</sup>

Digital: Having discrete states. Most digital logic is binary, with two states, on or off.

Central Processor Unit (CPU): Computer module in charge of fetching, decoding, and executing instructions. It incorporates a control unit, an Arithmetic Logic Unit, and related facilities (registers, clock, drivers). Computer: General purpose computing system incorporating a Central Processor Unit (CPU), memory, Input/Out-

put facilities and power supply.

Digital/Computer:, The field of electronics that employs either digital circuits or computer hardware and software or both.

Hardware: Any piece of data processing equipment is informally called hardware.

High-Level Language: Problem-oriented programming language, as distinguished from machine-oriented programming language. Examples are Basic and Fortran. Integrated Circuit: A circuit which is fabricated on a single chip of silicon. Initial integrated circuits contained less than one hundred semiconductors devices on a single chip.

Large Scale Integration (LSI): Technology by which thousands of semiconductors devices are fabricated on a .single silicon chip.

Machine Language: Set of binary codes, representing the instructions which can be directly executed by the processor.

Microcomputer: Complete system, including CPU, memory, Input/Output interfaces and power supply. The CPU is normally a Microprocessor.

Microprocessor: LSI implementation of a complete processor (Arithmetic Logic Unit / Control Unit) on a single chip.

Software: The programs that are entered in the computer:

The purpose of this study is to determine the kind of job skills required by a computer technologist and to develop course materials that will train electronic students in fundamental digital/computer technician skills. This study will not determine all the skills required

750.-

by an electronics technician but will limit the field to digital/computer electronics.

Many of the skill training techniques in the proposed digital/computer technology course can be applied to a range of levels from technician to engineer. However, this course was not meant to teach engineering design skills but fundamental skill development in digital/computer techniques.

The Dacum chart, prepared during this study, showed that there are specific mechanical skills required by a computer technologist. This aspect of training, mechanical skills, has not been included in the proposed Digital/ Computer Technology course. See Chapter VIII for recommendations regarding training of mechanical skills.

Related subjects (Math, Physics, Communications) are not covered by this study, however, a number of employers indicated the importance of fundamental skill development in math. For recommendations on communications skills see Chapter Vill.

#### LIMITATIONS

The final draft of the Dacum chart was not received until late February therefore it was impossible to receive imput from industries other than those that directly participated in chart development. Possibly the chart would more accurately reflect the digital/computer industry with

2,00

s E

÷F:

input from a broader spectrum of industries.

There was insufficient time between the completion of the study and its presentation to have representatives of the digital/computer industry comment on the course content. Before implementation of the Digital/Computer Technology course input should be sought from industry regarding course objectives.

No evaluation techniques for the teacher are included in the proposed digital/Computer Technology course.

Most of the learning activities have been field tested, however, lack of hardware has meant that some activities are presented without prior testing.

#### II HISTORY OF COMPUTERS

à

The earliest recorded digital instrument was the abacus, it was first used in Egypt about 460 B.C. The abacus evolved from the use of pebbles laid in rows on the sand and used for counting purposes. The pebbles were simply held together by a string to form the first abacus. In the middle ages the abacus moved from Europe to Asia and now is very popular in Russia, China and Japan.

The first automatic digital computer was Pascal's mechanical calculating device (1641).<sup>3</sup> Both addition and subtraction could be performed on Pascal's instrument. Later (1694) Leibniz advanced the design to do repeated additions and subtractions. Neither Pascal or Leinbniz were engineers (they were mathematicians), their machines were not well constructed and were sometimes not reliable.

Probably the most notable contribution to modern computers was made by Charles W. Babbage. Babbage is sometimes called the grandfather of modern computers. His first invention (1822) was a difference engine, it was used to facilitate the calculation of insurance tables. However his fame rests on the ANALYTIC ENGINE. This was considered by Babbage, in 1833, as a general purpose calculator as opposed to the specific purpose difference engine. Babbage saw his engine as composed of several smaller engines, each working together with the others, each performing his own separate chore: the "mill", which did the arithmetic: the "receiver" to take in information: the "printer" to print out information: a device to transfer information from one component to the other; and a "store" of information.<sup>4</sup> Unfortunately his idea was 100 years ahead of the technology, he spent the rest of his life working on the analytic engine, but without success.

Page 8

In 1890 the time required to process the United States census was reduced dramatically. The census was compiled with the use of a Hollerith computing machine. Essentially it was a card sorter with data supplied to the machine by hollerith cards. Hollerith's company eventually became the International Business Machines Corporation (IBM).

Howard Aiken, a math teacher with a doctorate in physics, combined with IBM and Harvard to build the first "electric" computer. This computer, completed in 1944, was called the Mark 1 and used relays for storage. The machine was very large and data was fed in by punched tape. The first "electronic" computer was built by Bckert and Mulchy at the University of Pennsylvania (1946). Called the ENIAC it could multiply two ten digit numbers in three one-thousandth of a second. It contained 18,000 vacuum tubes and occupied a room forty by twenty feet.

10

Probably the greatest contribution to computer programming was made by John von Neumann in 1946. His idea was to have both instructions and data stored in memory, this way the computer could be used to change its own program.

In 1948 Bardeen, Brattain and Shockley, working at Bell labs, developed the transistor. This event spelled doom for the vacuum tube and led to the miniaturization of electronic circuits. It is probably the most significant event in electronics in the first half of the twentieth century.

The Univac 1 (1950) was the first commercial computer, it was manufactured by Remington Rand.

The IEM 650 was the most popular computer of the 50's. The machine was widely used by the insurance, banking and accounting companies. It rented for \$50 per hour versus the more powerful IEM 704 at \$600 per hour. The 704 was a massive computer requiring a very large room for storage. In 1959 IEM had 90% of the computer market.

The latter part of the 50's saw the introduction of

Page 9

the transistorized computer. The 650 was replaced by the transistorized 1401, much smaller and faster. The 704 was replaced by the 7040 with a reduced size and price, and increased speed.

In 1964 IBM introduced the model 7010, an upgrade from the 1401 and a new series of computers, the IBM 360 family of computers. This was the first family of compatible computers ranging from small to large. Essentially one could start with a small processor, 33,000 additions per second, and using the same software upgrade to a larger processor, 2,500,000 additions per second. With the IBM 360 came integrated circuits.

The 1970's saw the introduction of the IBM 370 family of compatible computers. They introduced large scale integration to both the arithmetic/logic units and the memory. In addition, "most System/370 models, for example have "Virtual Storage" capability that magnifies the capacity of main memory many times, and enables users to work economically with millions of characters of information."<sup>5</sup> BIRTH OF THE MICROCOMPUTER

Datapoint, a manufacturer of computer terminals, wanted to have a computer terminal that contained a small computer, that is a "smart" terminal. They contacted Texas Instruments and Intel, leaders in microelectronics, to develop such a system. Intel developed a system around the 8008 microprocessor, however, Datapoint dropped the idea of a single-circuit computer terminal. Intel was left with the technology but no customer. They decided to market the 8008 microprocessor. Since 1973 they have sold more than three million.<sup>6</sup>

Following the 8008 came the Intel 8080; the Motorola 6800, the Ziloz Z80, and the MOS Technology 6502. These are all 8 bit microprocessors as opposed to the 16 and 32 bit central processors used by Digital Equipment Corporation and IBM.

Micro Instrumentation and Telementry Systems (MITS) sold the first microcomputer, based on the 8080. These were Kits, first advertised in Popular Electronics, January 1975, they expected to sell 800 in one year. On the Friday after Popular Electronics was published they received orders for over 400, they went on to sell several thousand.

Radio Shack with its TRS-80, based on the Z-80, was introduced in 1977 and within one year had sold in excess of 100,000.

In 1977, Commodore Business Machines introduced their microcomputer, the Commodore PET based on the 6502, and within one year sales had passed the 25,000 mark.

Several other companies (Apple, Compucolor, Heathkit) are marketing microcomputers based on the microprocessor. Within the past two to three years sales have passed several thousand.

#### SUMMARY

Computers have essentially passed through four generations, Vacuum tubes, Transistors, Integrated Circuits, and Large Scale Integrated Circuits, see Table 1. Until the late seventies the history of computers has essentially been the history of IBM. However, as the seventies came to a close the sales volume of microcomputers equalled the combined sales of IBM and all other models of mini and mainframe computers.

Predictions for the future are that the field will be divided up into two distinct classes:

1. Large volume of sales of microcomputers manufactured by a number of manufacturers.

2. Very few large mainframe computers manufactured by a small number of companies dominated by IBM. 7

The following chart shows how data processing costs and processing time have declined during the past two decades. It represents a mix of about 1700 computer operations, including payroll, discount computation, file maintenance, table lookup, and report generation. Figures show costs of the period not adjusted for inflation.

|                    | 1955                                             | 1960                                                    | 1965                                                                                                                   | 1976                                                                                                                                          |

|--------------------|--------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Cost*              | \$14.54                                          | \$2.48                                                  | \$.47                                                                                                                  | \$.20                                                                                                                                         |

| Processing<br>Time | 375 sec.                                         | 47 sec.                                                 | 37 sec.                                                                                                                | 5 sec.                                                                                                                                        |

| Technology         | Vacuum tubes<br>Magnetic cores<br>Magnetic tapes | Transistors<br>Channels<br>Faster cores<br>Faster tapes | Solid Logic<br>Technology<br>Large, fast<br>disk file<br>New channels<br>Larger, faster<br>core memory<br>Faster tapes | Monolithic memory<br>Monolithic logic<br>Virtual Storage<br>Larger, faster disk<br>files<br>New channels<br>Advanced tapes<br>Microprocessors |

| Programming        | Stored program                                   | Overlapped<br>input/output-<br>Batch process-<br>ing    | Operating<br>system<br>Faster batch<br>processing                                                                      | Virtual Storage<br>Advanced operating<br>systems<br>Multiprogramming<br>Batch/on-line<br>processing                                           |

. ut

. . .

1

Page

13

\* Cost per 1700 operations

18

÷

# III HISTORY OF ELECTRONICS TRAINING

# REGIONAL VOCATIONAL SCHOOLS

in

#### in

#### NOVA SCOTIA

The first program in electronics training offered in Nova Scotia was at the Yarmouth Regional Vocational School. The course was called Electrical and Radio Repair and was taught by George Williams. George is presently Vice-principal at the Nova Scotia Institute of Technology. The goal of the course was to develop skills in radio repair based on vacuum tube technology. The first class enrolled in the three year program in September 1950 and graduated in June 1953.

The second program in electronics was offered by the Halifax Regional Vocational School. This was a course in radio repair similar to the course in Yarmouth. Skills taught were confined to the vacuum tube field. The first teacher was Gerry O'Malley now the Principal of Dartmouth Regional Vocational School.

In 1954 the course content was up-dated in both schools to include television repair and the course was changed to Electronic (Radio and TV repair). In 1962 four additional Vocational Schools were opened in Nova Scotia, each had an Electronics course. The course was similar to that taught in Halifax and Yarmouth and was called Electronic (Radio and TV). The technology was vacuum tube and the goal of the course was to teach basic electronics with Radio and Television receivers used as the training vehicle. It was felt that general skills in electronics could be taught using radio and television as a model and those skills would then be transferable to other areas of electronics. These new schools were located at Springhill, Stellarton, Sydney and Kentville.

In the mid 60's transistors were introduced to the school curriculum. At that time Halifax revised their curriculum and concentrated their studies in the semiconductor field. The remaining schools modified their curriculum to include semiconductor technology.

During the years 1968-69 seven new vocational schools were opened, each with a course in electronics. These new schools were located in Shelburne, Bridgewater, Dartmouth, Middleton, Truro, Port Hawkesbury and Windsor. All the schools offered a program in Electronics (Radio and TV) similar to that expressed above. In addition Dartmouth, Bridgewater and Kentwille offered a course in Electronics (Navigation). This course was designed to teach the skills knowledge and attitudes required to secure employment in the marine navigation field. The technology employed in both courses was both tube and transistor.

Page 16

It appears that in the late 60's three closely related programs in Blectronics were offered to the youth of Nova Scotia:

1. Electronics (General using radio and TV as a training vehicle.

2. Blectronics (Navigation) using radio, TV and Navigation equipment as the training vehicle.

3. Electronics with special emphasis placed on pulse and switching circuits at Halifax Regional Vocational School.

In the early 70's integrated circuits were introduced into the electronics program. It is not clear how this affected training however, some schools, Halifax and Truro, became more involved in projects employing integrated circuits (IC). The navigation course at Kentville, the Blectronics (Radio and TV) at Dartmouth and the Blectronics course at Windsor were dropped. In Bridgewater the two Electronics courses were merged.

#### SUMMARY

992

Until the mid or early 70's electronic programs have been able to keep up with the changes in electronic technology. With the introduction of Large Scale Integrated circuits and Microprocessors electronics training programs have fallen behind the technology. Normally this would not cause a problem because the introduction of new training materials usually lag the introduction of new technology. However, the application of microprocessors in both industry and consumer products has taken place at such a rapid pace that this typical lag must be shortened.

The 60's have seen the demise of the vacuum tube. The 70's have seen discrete transistors take the same route as the vacuum tube. Therefore, IC and LSI will and should become the training vehicle for electronics in the 80's.

After reviewing the history of electronics in Regional Vocational Schools it would appear that renewal in program materials is required. The purpose of this thesis is to present a rationale for such a renewal and to develop. a course of study based on integrated circuits and large scale integrated circuits that would be applicable to Vocational Schools in Nova Scotia.

Page 17

### EV PROJECTIONS FOR THE COMPUTER INDUSTRY

It is very difficult to predict trends in an industry that has undergone such rapid change, especially in the last 5-10 years. However, three trends have been emerging in the latter part of the 70's, they are:

1. Dramatic increase in the sales of microcomputers.

2. Data Communications

3. Word Processing

MICROCOMPUTERS

Traditional methods of selling computers will change. Rather than have a computer salesman order you a computer, most computers (90% by 1990) will be sold out of computer stores. The world's first computer store, "The Computer Store", was opened in 1975. By the end of 1978, over 700 stores were opened in the United States alone. This rapid growth is continuing. Digital Equipment Corporation, the world's leading minicomputer manufacturer, recently opened a computer store in the "Mall of New Hampshire", Manchester, N.H. It was such a success that they have planned or are opening several more in the Eoston area.

Computer stores have become successful for two reasons:

1. They give you a chance to examine a variety of different systems before you buy.

2. They eliminate sales representatives, who typically cost forty percent of what you pay for the computer system.<sup>9</sup>

Computer stores will almost exclusively sell micro-

In addition to microcomputers being readily available to the public, especially the businessman, they can now, or will be able to in the future, perform most or all of the functions of a mini or small mainframe computer, and at a much lower cost. In fact, electronics already exists to make microcomputers as powerful as a mainframe. The development of the Intel 8086, is an example of the tremendous progress made in microcomputers.

Prediction: By the mid or late 1980's, ninety percent of all computer sales will be microcomputer systems or their equivalent. The remaining ten percent will be the largest, most powerful and most expensive mainframe computers. These mainframe computers will be dedicated to such things as:

1. Difficult computations associated with weather forecasting and geological data analysis.

2. Control of large information banks.

**4**00

3. Data processing for state and federal government agencies (for example, the Social Security Administration).<sup>10</sup>

Sales of microcomputers will increase at a very rapid rate, and will shortly exceed 1 million per year. At a recent international computer conference held in Wolfville, Nova Scotia a Pentagon computer expert predicted that computers will become the world's largest industry in the near future, dwarfing North America's automobile industry.

## DATA COMMUNICATIONS

The merger of computers and communications continues at a relentless speed, making a distinction between the two terms becomes more difficult every year. As the boundaries between data processing and communications continue to merge, it may well be that data processing firms will offer telecommunication services as well. Electronic mail appears to be a real possibility. It is expected that the main competition in data communication for International Telephone and Telegraph (ITT) and American Telephone and Telegraph (AT & T) will come from IBM and Xerox Corporation.

Canada is presently one of the world leaders in data communications. The Canadian Telidon "alpha-graphic" approach was developed by the Communications Research Centre, a branch of the Department of Communications.

The Telidon system is made up of four major elements:

1. User terminals

2. Information supplier terminals

3. The telephone network and associated data networks such as data pac and data route

4. A computer for information storage, retrieval and switching centre.<sup>11</sup>

A modified version of Telidon "Vista" is being field tested by Bell Canada Ltd. and Department of Communications.

The Department of Communications and Bell Canada are co-sponsoring trials that will involve 1000 Canadian made user terminals and up to 100,000 pages of on-demand information, for display on home or office color T.V. sets. It will be one of the world's most advanced trials of Videotex, the internationally recognized term for such public, network based information systems.<sup>12</sup>

The Vista system, essentially identical to the Telidon, will employ a conventional Color Television, a control unit to couple the T.V. with a normal telephone and a hand held key pad. Pressing a designated key will convert the T.V. set into a Vista interactive information user terminal. The user will then have access to a Data base of a PDP 11/60. Prime user groups of the system will be the home users and the business community. In business applications, a full alpha-numeric keyboard will be used rather than a key pad.

Projections are that this kind of system will make massive amounts of information readily available to the general public. Through such systems as "the Source", / it is now possible to connect your home computer, Radio Shack, Pet, etc., to a large main frame computer in Washington, D.C. This means that your microcomputer has access to literally hundreds of data banks. The largest growth in the computer and computer related industries will take place in a data communications.

Another Canadian company, AES Data, Ltd., world leaders in word processing systems, are combining with CNCP to develop data communications for the business community.

WORD PROCESSING

Word processing is a combination of hardware and software. Usually it consists of a micro or minicomputer with dual floppy, disc, a Cathode Ray Tube (CRT) and a character printer. In addition the computer contains a software package that allows the operator to type text into the computer and manipulate the text so that it can be printed out in some pre-determined manner. The operator can append clauses, adjust page length, put data into alphabetical and numerical order, columnize, move text, insert and delete, all viewed on a CRT. To review text or processed pages, the operator simply scrolls a cursor either up or down. Files, that is text are stored on floppy disc.

3

Communicating word processors, data communications, allow the boss to call up a typed letter on his own CRT terminal, do his own editing and then send the electronic letter to, ultimately anywhere in the world. Infotex, for example, will be capable of transmitting a 300 word letter in seven seconds, like a postman moving near the speed of light.<sup>13</sup>

ABS Data of Montreal, formed in 1974 are world leaders in word processing. Projected sales for 1979 are in access of 125 million dollars. It appears that the paperless office has really caught on with business. However, only 15 percent of the market is presently being serviced, therefore, the 80's should see a tremendous growth in word processing.

The large scale marketing of computers means that thousands of new jobs will be created to install and

Page 23

maintain microcomputers and peripherals. In addition the rapid explosion of word processor equipment, essentially a micro or minicomputer will mean additional maintenance jobs. The fundamental skills required for microcomputer maintenance can and should be taught at Regional Vocational Schools.

The rapid expansion of data communications will provide additional jobs. Many of these skills will be the same as those required for digital/computer electronics. However, additional skills in broadband communication will be required, these should be investigated by the Department of Education and the appropriate training provided for the youth in Nova Scotia.

## V INDUSTRY REQUIREMENTS, DACUM CHART

Before developing or reviewing curriculum for training Digital/Computer technicians it was necessary to determine the kind of skills a technician employed in the industry should possess. The following tools were considered in order to find out what these skills were:

1. Inquiry forms filled out in the presence of the questioner. These forms are normally called schedules.

2. The questionnaire, which is probably the most used and abused of data gathering devices.

3. The interview where the questioner asks oral questions and notes or tape records the response.

The first two were considered inappropriate to conduct an industry survey. I discovered that industries are bombarded by questionnaires and they do not normally have the time or interest to respond.

Serious consideration was given to the interview, however, this technique is very time consuming and one of the most difficult to employ successfully. The interviewer must be skilled in asking a sequence of questions and make stimulating comments that will produce the desired results. It would appear that considerable training is required to make this method successful.

The survey problem was discussed with Dr. D.L. Burt, Director of Instructional Services, Nova Scotia Teachers College. He suggested that I consider an occupational analysis based on the Dacum model.

Developing a Curriculum (DACUM) is a system that encompasses three main components:

1. It is an <sup>4</sup>approach to occupational analysis.

2. It is an approach to planning and developing training based on the analysis.

3. It is an approach to training program operation.

The result of an occupational analysis is a chart (Dacum Chart) produced by a committee of "experts" who participate in a three day workshop. The purpose of this workshop, under the guidance of a skilled co-ordinaton, is to identify the skills associated with their occupation. These skilled experts are normally technicians or working foremen employed in the occupation to be analyzed. In this case they would be technicians in the occupational field of Digital/Computer Electronics.

The selection of the Dacum process to determine Digital/Computer technician skills was based on the following:  $\zeta$  1. Several industries and educational institutions rely on the Dacum method for occupational analysis of a trade or technology. A few of these institutions are:

Nova Scotia Institute of Technology (N.S.I.T.) Adult Vocational Training Centers in Nova Scotia Holland College

Nova Scotia NewStart Inc. Nova Scotia Land Survey Institute Scott Paper Company Ferguson Industries National Sea Products

2. The Dacum method of occupational analysis has been used by the Electronics Technology program at Holland College since its inception. Sorenson in his article, A Summary of the Research "Entry Level Skills-Electronics", describes the application of a Dacum chart on Electronics Technology.<sup>15</sup> This survey illustrates the importance of the Dacum method of occupational analysis at Holland College.

3. Local expertise was available for developing a Dacum chart. The Adult Vocational Education program of the Department of Education has a resource facility, under the direction of Mike Kent, for developing Dacum Charts. This facility has developed charts for more than

twenty occupational fields, typical are: Blectronic Repair; Radio Announcing and Stenography.

An application, in conjunction with the Nova Scotia Institute of Technology, was made to the Department of Education, Adult Education for approval to construct a Dacum chart for the occupational field of Digital/Computer Electronics.

The application was approved, January 28, 29, and 30th were selected as the days to construct the chart. Jim MacLennan, Department of Education, Adult Education was appointed project co-ordinator.

The following companies provided workshop participants:

l. Department of National Defence (Dockyard),

participant Robert George.

2. Bedford Institute of Oceanography, participant Sidney Specce.

3. Control Data Corporation, participant Edward Billerwall.

4. Maritime Telephone and Telegraph, participant Ernest MacPherson.

5. Defende Research Eastern Atlantic, participants Vance Crowe and Howard Hart.

6. National Cash Register, participant Gordon Heffler.

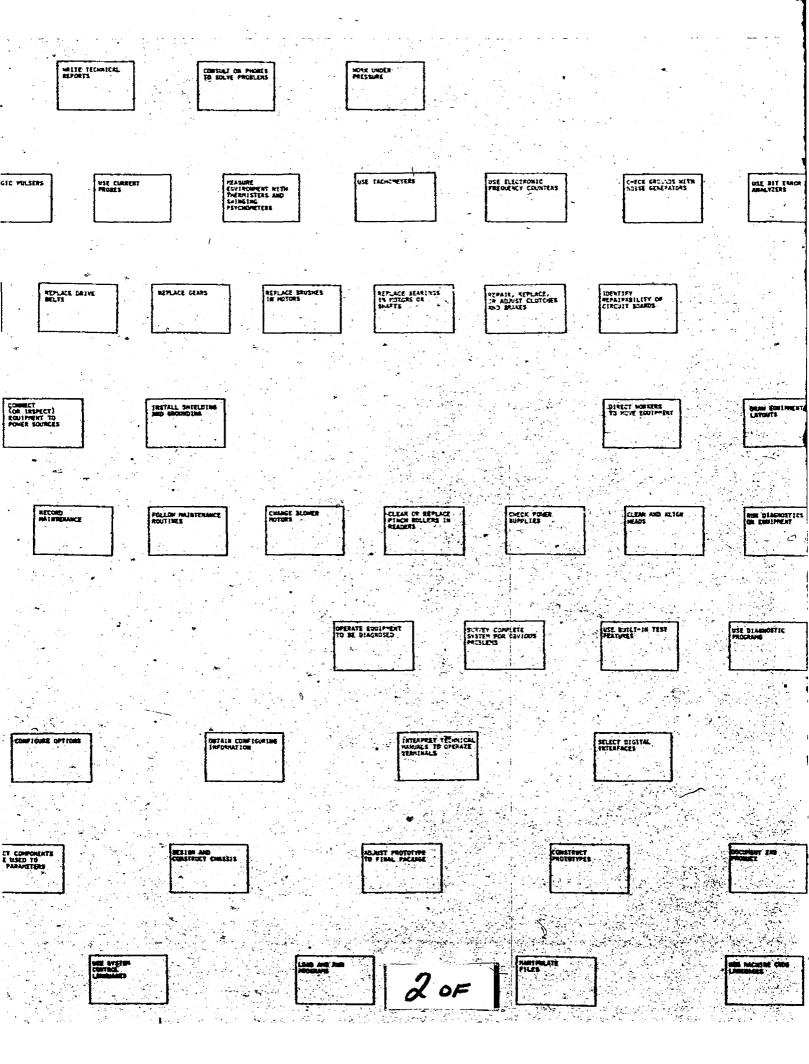

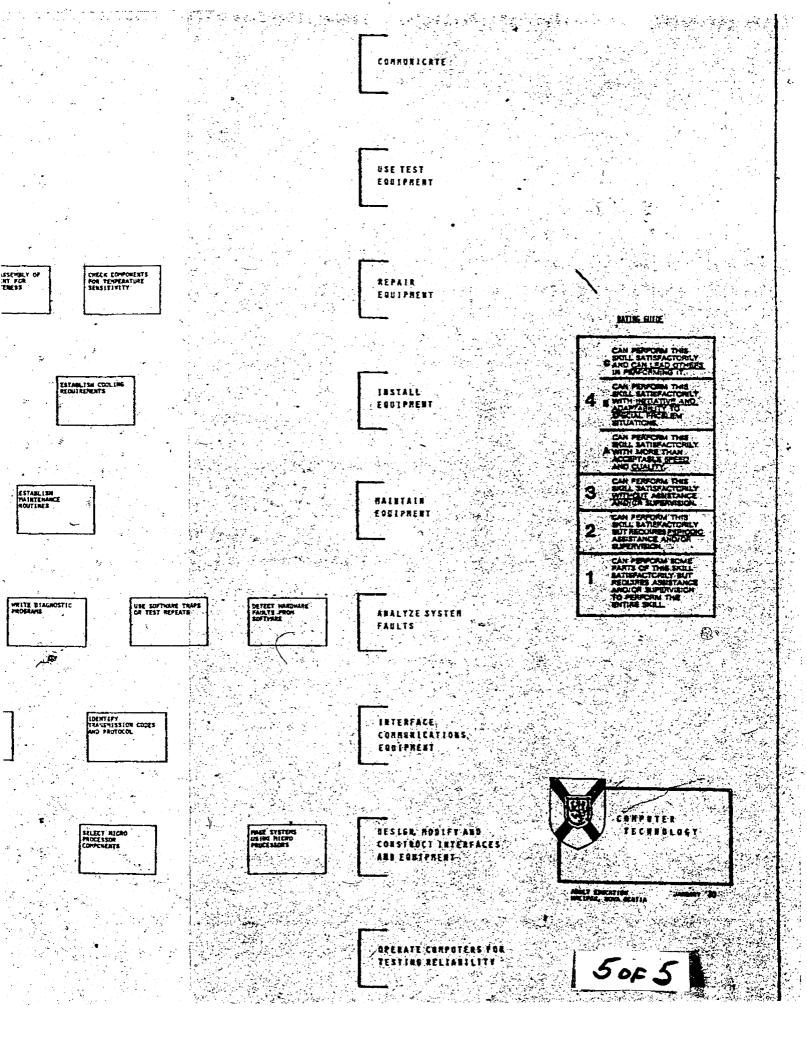

Table 11 is the Dacum Chart containing the skills identified in the workshop. These are actual on the job skills and are representative of the Digital/Computer industry. This chart can be used as a blueprint in developing course materials to train Digital/Computer technicians. That is, fundamental skills taught in Vocational and technical schools should provide a solid background for actual on the job skills performed by industry.

| WORK A                                           | AS & MEMORY<br>TEAM                            | READ BORNATICS                          | ALTRESENT<br>CONTANY O | TOUR<br>DR FIRM                                 | COMPLETE TECHNICAL REPORT FOUNS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | WELTE TECHNICAL REPORTS                                   |                                                                         |

|--------------------------------------------------|------------------------------------------------|-----------------------------------------|------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------|

|                                                  |                                                |                                         |                        |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -                                                         |                                                                         |

|                                                  |                                                |                                         |                        |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           |                                                                         |

|                                                  |                                                |                                         |                        |                                                 | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                           |                                                                         |

| Dat N                                            | INCLUMETERS                                    | USE DIBITAL YOLT                        | BEE OFEITTORCOLE       | USE LOGIC PRO                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | IC PULSERS                                                | - 1001                                                                  |

|                                                  |                                                |                                         |                        |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           |                                                                         |

| •                                                |                                                |                                         |                        |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           | 4                                                                       |

|                                                  |                                                |                                         | •                      | •                                               | алана <b>на</b> .<br>Спорти                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                           | -                                                                       |

| 504,200                                          |                                                | WHICH SER                               | MAKE SOLDERLESS        | FOLLOW SPECIAL<br>HANDLING<br>TECHNIQUES AROUND | FOLLOW<br>HANUFACTURERS"<br>POULPHENT HANDLING<br>INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | REPLACE DRIVE<br>BELTS                                    | REPLACE                                                                 |

|                                                  |                                                |                                         |                        | SPECIAL<br>CONCOMENTE                           | TRATEUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                           |                                                                         |

|                                                  |                                                |                                         |                        |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           | · · · · · ·                                                             |

|                                                  |                                                |                                         |                        |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           |                                                                         |

|                                                  |                                                |                                         |                        | CABLE PO<br>TOOSTWER                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CONNECT<br>(OR INSPECT)<br>EQUIPMENT TO<br>FORCE SQUARCES | INSTALL 4                                                               |

|                                                  |                                                |                                         | <b>N</b>               |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | EQUIPMENT TO<br>POWER SOUNCES                             |                                                                         |

|                                                  |                                                |                                         |                        |                                                 | <b>ب</b> ر المحمد المحم<br>المحمد المحمد |                                                           | •                                                                       |

|                                                  |                                                |                                         |                        |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           |                                                                         |

|                                                  | caniment.                                      | CLEAN ON CHANSE                         | CLEAN PRINT DRUPS      | CLEAN AND HANDLE                                | CLEAN AND MANDLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | AFCORD<br>MATENERANCE                                     | FOLLOW MI<br>ROUTINES                                                   |

|                                                  |                                                |                                         |                        |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           | e e e e e e e e e e e e e e e e e e e                                   |

|                                                  |                                                |                                         |                        |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | an a                  | · · · · · · · · · · · · · · · · · · ·                                   |

|                                                  |                                                |                                         |                        |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | and and a                                                 |                                                                         |

|                                                  |                                                |                                         |                        |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           |                                                                         |

|                                                  |                                                |                                         |                        |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | nite<br>Jan                                               |                                                                         |

|                                                  | ار میں اور |                                         |                        |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           |                                                                         |

|                                                  |                                                |                                         |                        |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           |                                                                         |

|                                                  |                                                |                                         |                        | RALE UP INTERF                                  | ACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | COMPTONE OFTIME                                           |                                                                         |

|                                                  |                                                |                                         |                        |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 |

|                                                  |                                                |                                         |                        |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           |                                                                         |

|                                                  |                                                |                                         |                        |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           |                                                                         |

|                                                  |                                                |                                         |                        | SE-INS PROPERTY                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           |                                                                         |

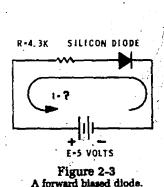

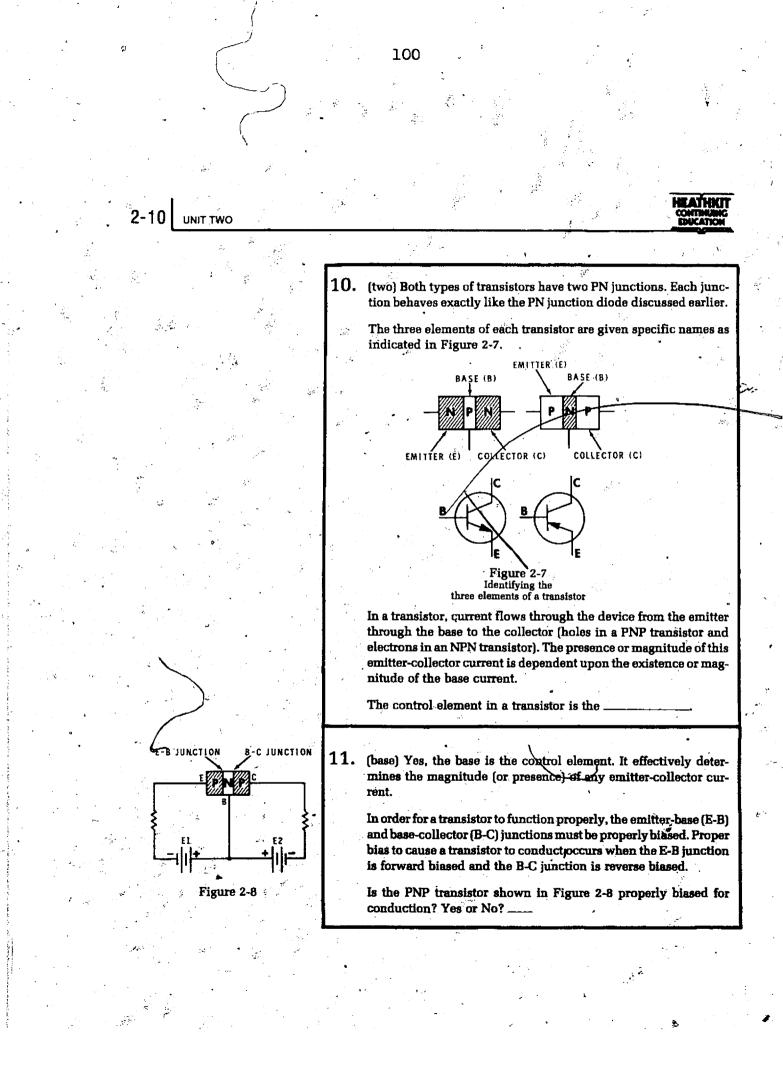

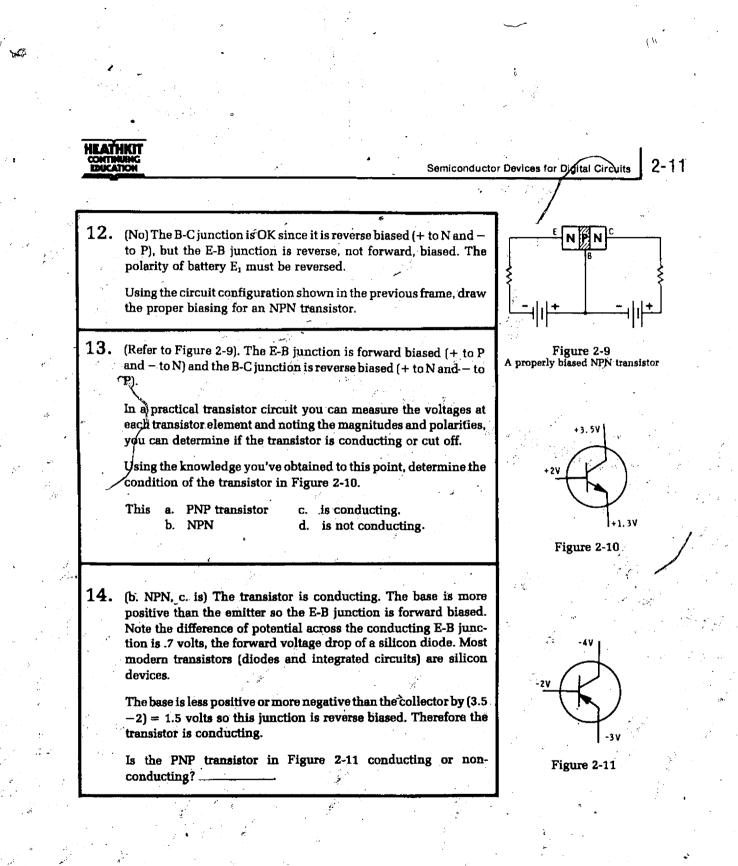

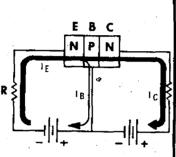

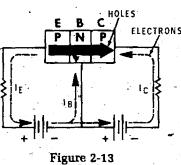

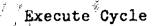

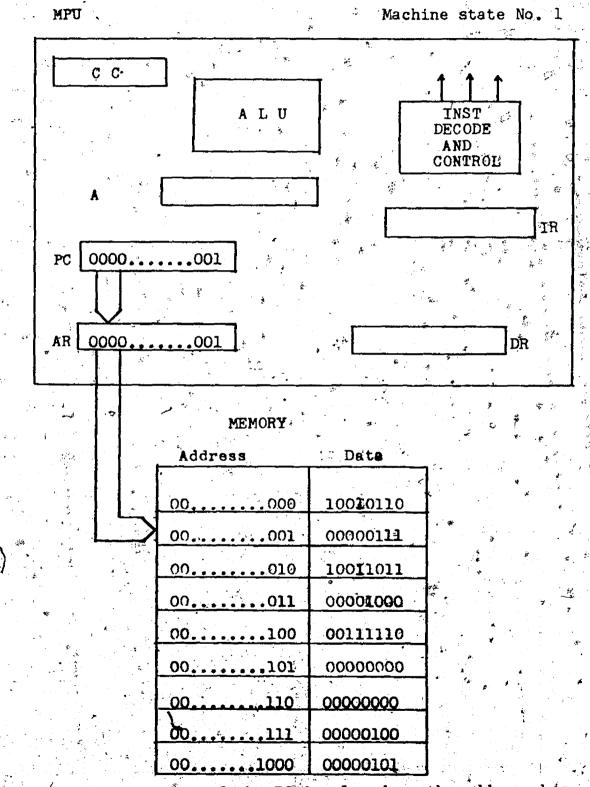

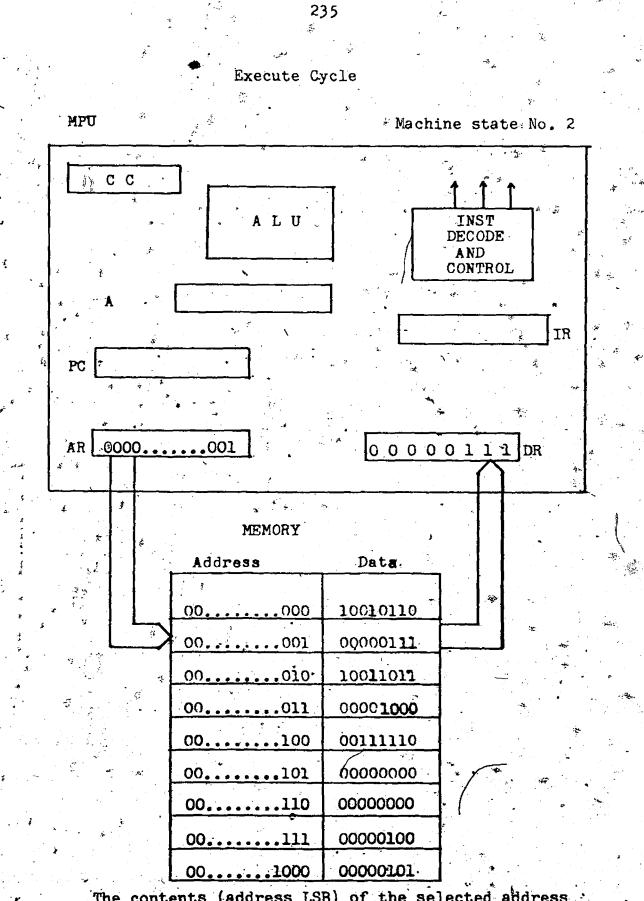

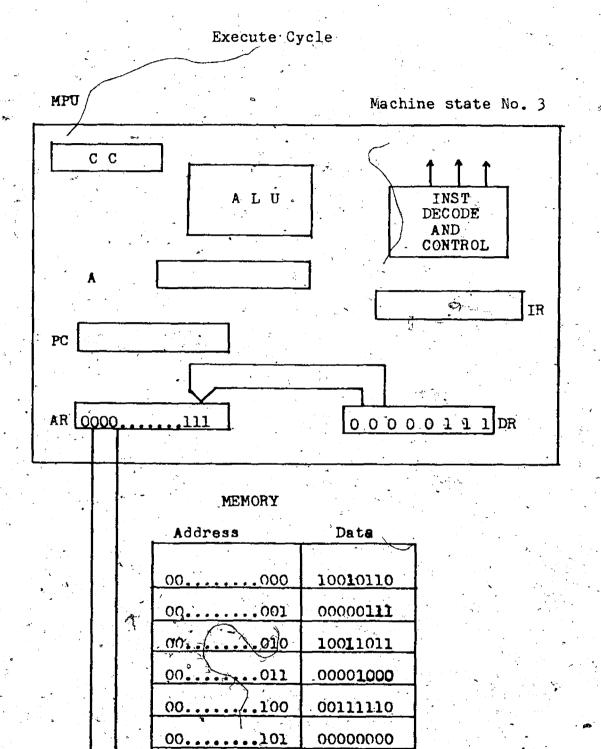

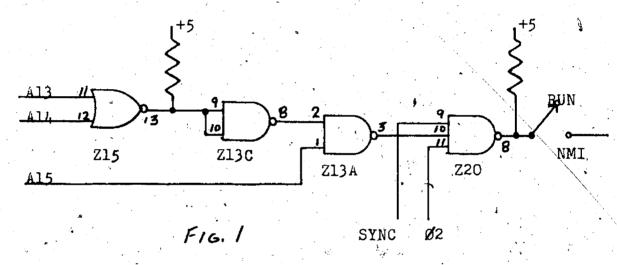

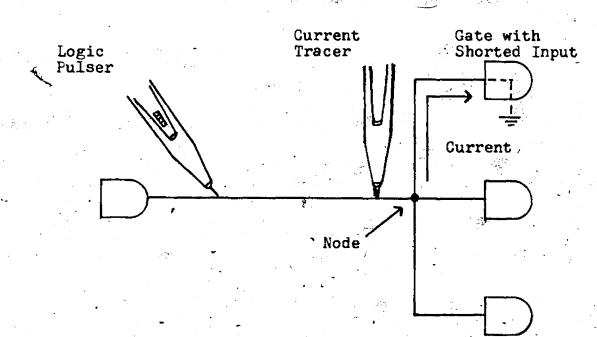

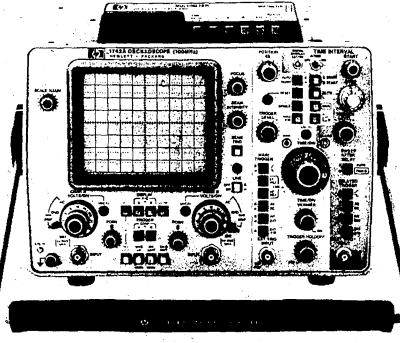

|                                                  |                                                |                                         |                        |                                                 | IQ AL<br>RLT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | T COMONENTS<br>L USED TO<br>PARAMETERS                    | BESI                                                                    |